# Experimental test bench for GaN multilevel topologies

${\tt Degree\ programme: Master\ of\ Science\ in\ Engineering\ |\ Specialisation: Energy\ and\ Environment}$

Thesis advisors: Timothé Delaforge, Prof. Dr. Sébastien Mariéthoz

Expert: Alain Lacarnoy (Schneider Electric)

In this thesis, a multilevel topology was studied. After optimizing the layout, the prototype was built and commissioned. Two different topologies are mounted back-to-back in order to make experimental comparisons. Some specificities of this type of converter were investigated, such as the precharge, the voltage balancing or the discharge.

### Context

The recent improvements in semiconductors, especially in GaN and SiC components, offer new opportunities to make high efficiency converters in the small and medium power range. The multilevel topologies were used to exceed the voltage limits of traditional components in high voltage technique, whereas today, we try to merge them with new transistors technologies to take up new energy challenges.

# Goal

The aim of this project is to develop a test bench with two different multilevel topologies in order to investigate their behaviour in operation and compare them experimentally. The first converter is a "Flying Capacitor", a prototype that already existed in the PELaB. The second one is a "Stacked Multicell Converter", this prototype had to be developed.

# **Starting point**

In a previous project, the flying capacitor converter was studied and a new layout was developed. The stacked multicell converter was designed using an optimization software from PELab. For the sake of having a common basis for comparisons, the prototypes use the same GaN technology and the same power rating.

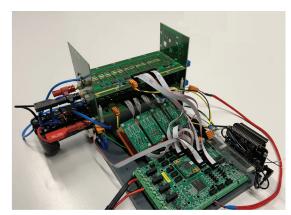

Test bench prototype

## **Implementation**

Investigation of SMC operation and control was done on simulation software. Then, to achieve a high efficency converter, an optimal layout was proposed to the commutation cells with the GaN FET to dramatically reduce parasitics. All safety rules were respected to design the SMC PCB board. The FPGA modulator was adapted to SMC special switching pattern to have a correct control on the converter. Finally, the two topologies were put back-to-back to loop the power between the converters so the supply provides only the losses and no need for a load. The security and start/stop processes were validated, just like the voltage balancing, which is specific to these converters. A full investigation was led on the converters over a large domain of operation. Main task was to fine tunning the filters to improve the regulation of the converter and also to resolve EMI problems.

Eric Rudolf Donzé erdonze@gmail.com

### **Results and outlook**

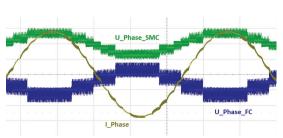

The objectives were accomplished. The converters work in safe operation, the validation of the new layout is done and the voltage balancing on the two topologies is efficient. Loss analysis was performed allowing comparisons of experimental results with simulations. Futher tests will be done at higher power.

Voltage and current waveforms of the test bench