BU

## **UNICONTROL** Basissystem

Fachgebiet: Embedded Realtime Betreuer: Roland Brun

Experte: Mario Giacometto

Industriepartner: Wyssen Seilbahnen AG, Reichenbach i.K.

Das Projekt beschäftigt sich mit der Entwicklung eines FPGA-Designs als Basissystem für ein universelles Steuerungssystem. Zudem beinhaltet es eine Mikrocontroller-Software, welche das FPGA-Design steuert. Das Projekt entstand in Zusammenarbeit mit Wyssen Seilbahnen AG.

Für die Produkte zur künstlichen Lawinenauslösung der Firma Wyssen wird im Hause ein universelles Steuerungssystem für sicherheitsgerichtete Anwendungen entwickelt. Das Steuerungssystem soll universell für alle Maschinen von Wyssen einsetzbar sein, daher der Name «UNICONTROL».

Das umfangreiche Projekt wurde für die Entwicklung in viele kleine Teilprojekte unterteilt. Ein solches Teilprojekt ist das «UNICONTROL Basissystem», welches im Rahmen einer Bachelorthesis realisiert wurde.

Das Basissystem mit sechs Ausgangsschaltungen für Lastströme bis 2A beinhaltet ein FPGA und einen Mikrocontroller. Die Treiber und AD-Wandler der Ausgangsschaltungen sind am FPGA angeschlossen. Die Messdaten werden im FPGA in Echtzeit aufbereitet und über eine serielle Schnittstelle zum Mikrocontroller übertragen. Die Steuerdaten für die Ausgänge werden über dieselbe Schnittstelle zum FPGA übertragen, welches daraus die Signale für die Leistungstreiber erzeugt.

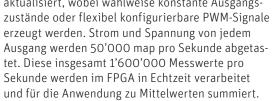

Während der Thesis wurde ein bestehendes VHDL-Design auf die Hardware portiert, bereinigt und erweitert. Das Resultat ist ein funktionsfähiges Design, das 16 unabhängige Ausgänge steuern und messen kann. Die Steuersignale werden alle 500 Nanosekunden

Reglerantwort des Stromreglers mit Anti-wind-up

aktualisiert, wobei wahlweise konstante Ausgangs-

Optional kann für jeden Ausgang ein unabhängiger Regelkreis eingeschaltet werden, der den Laststrom autonom regelt. Der verwendete Regler ist ein Integralregler mit einstellbarer Verstärkung und einem Anti-wind-up Mechanismus. Die Reglerantwort auf ein Rechtecksignal ist im Bild 1 erkennbar.

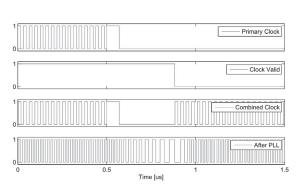

Weiter wurde im Projekt ein redundantes Taktsystem sowie ein Safety-Fallback als automatische Systemreaktion bei einem schwerwiegenden Fehler entwickelt. Die Reaktion des Taktsystems auf einen kompletten Ausfall der primären Taktquelle ist in Bild 2 erkennbar. Das System ist in der Lage den Ausfall innerhalb von 500 Nanosekunden zu erkennen und auf den sekundären Takt umzuschalten.

Der Softwareteil der Thesis beinhaltet ein kompaktes System, welches die Ausgänge auf hohem Niveau abstrahiert und deren simpelste Verwendung ermöglicht.

Benjamin Meier

Reaktion des Systems bei Ausfall der primären Taktquelle