Optimierender Zellensortieralgorithmus für einen MMC-Modulator

- Degree programme: BSc in Elektrotechnik und Informationstechnologie

- Author: Dominic Joshua von Bergen

- Thesis advisor: Prof. Dr. Torsten Mähne

- Expert: Stefan Bieser

- Industrial partner: ABB Power Grids Switzerland Ltd. Turgi

- Year: 2020

Eine moderne Spannungswandlertopologie, welche in der Energiebranche verwendet wird, ist der modulare Mehrstufenumrichter. Das Ziel dieser Arbeit war es, einen effizienten Sortieralgorithmus zum Selektieren der zu schaltenden Zellen zu entwickeln und in VHDL zu implementieren. Dieser wurde in das Gesamtsystem integriert und erfolgreich im Labor getestet.

Ausgangslage

Die ABB entwickelt Spannungswandler für hohe Spannungen und Ströme. Zu den Anwendungsgebieten solcher Wandler gehört die Netzstabilisierung oder auch die Frequenzumrichtung für Eisenbahnnetze. Eine der Wandlertopologien, welche heutzutage verwendet wird, ist der modulare Mehrstufenumrichter (englisch: Modular Multilevel Converter - MMC, Abb. 1). Diese Art Wandler ist aus einer Vielzahl kleinerer Schaltzellen aufgebaut. Um Netzspannung in hoher Qualität zu erzeugen sowie Verluste und Ausfälle zu minimieren, müssen die einzelnen Schaltzellen korrekt angesteuert werden.

Aufgabenstellung

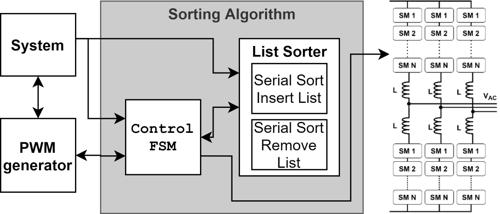

Das Ziel dieser Arbeit war die Entwicklung eines Sortieralgorithmus in VHDL, welcher auf Basis des überwachten Zustandes der Schaltzellen entscheidet, welche Zellen als Nächstes durch den Modulator aktiviert oder deaktiviert werden sollen. Dazu gehörte der Entwurf und die Implementierung des Hardwareblocks, seine Integration zusammen mit dem bereits in der Projektarbeit entwickelten Pulsweitenmodulator in das MMC-Gesamtsystem sowie Tests im Labor.

Realisierung

Zu Beginn wurde ein Sortieralgorithmus mit einem begrenzten Funktionsumfang implementiert. Mit diesem sollte die Grundfunktion simuliert und getestet werden. Deshalb wurde auf einige Zusatzfunktionen verzichtet und auch als Sortierverfahren nur ein einfacher Bubble-Sort-Algorithmus verwendet. Nachdem so bestätigt werden konnte, dass das Konzept umsetzbar und funktionstüchtig ist, wurde der Sortieralgorithmus schrittweise verbessert. Nebst den Zusatzfunktionen wurde das Sortierverfahren durch eine erheblich schnellere serielle Methode ersetzt. Auf Basis der gemachten Erfahrungen konnte die VHDL-Implementierung weiter optimiert werden und so deutlich an FPGA-Ressourcen gespart werden. Sämtliche Anpassungen und Verbesserungen wurden mit Testbenches simuliert und im Labor auf einem Echtzeitsimulator getestet.

Ergebnisse

Das entworfene Sortierverfahren funktioniert für eine beliebige Anzahl von Zellen. So kann als Beispiel eine 32 Einträge lange Liste mit Zellenzuständen innerhalb von 35 Taktzyklen sortiert werden. Um die Schaltzelle einzusetzen, werden im Normalbetrieb vier weitere Zyklen benötigt. In diesen vier Zyklen wird überprüft, ob eine Zelle defekt ging, ob eine Zelle eingesetzt werden muss und entschieden mit welcher Polarität dies geschehen soll. Von der Anforderung einer neuen Schaltzelle bis zum Schaltkommando werden 39 Taktzyklen benötigt. Der Ressourcenverbrauch konnte durch die optimierte Variante von 7839 LUTs auf 5246 LUTs reduziert werden. Dies entspricht einer Einsparung von 33 Prozent. Abb. 2 zeigt die Zellspannung und die Vorgabe der Anzahl aktiver Zellen während eines Labortests des Sortieralgorithmus im Gesamtsystem.