ASIC-Workflow für digitale STSCL-Schaltungen mit differentieller Signalübertragung

- Degree programme: BSc in Elektrotechnik und Informationstechnologie

- Author: Marc Simon Lochbrunner

- Thesis advisor: Prof. Dr. Marcel Jacomet

- Year: 2022

Zum Aufbauen von integrierten Schaltungen, basierend auf der ultra-low-power STSCL-Topologie, sind spezielle Hilfsmittel nötig. Nur damit ist es möglich, die differentiellen Leiterbahnen zwischen den STSCL-Logikgatter, in einem automatisierten Prozess, zu generieren.

Aufgrund des tiefen Leistungsverbrauchs und der hohen Toleranz gegenüber Prozessschwankungen, stellt die Subtreshold Source-Coupled Logik eine vielversprechende Alternative zur CMOS-Logik dar.

In der Medizinaltechnik ist es ein Ziel, die Energie zum Betreiben eines elektronischen Implantates, direkt aus dem menschlichen Körper oder seiner Umgebung zu gewinnen. Solche Energy Harvesting-Methoden sind in der Lage, 5-10uW abzugeben, wobei die Ausgangsspannung nicht konstant ist. Da zur Versorgung einer STSCL-Schaltung, im Gegensatz zu CMOS, kein Spannungsregler benötigt wird, bietet sich die STSCL für ULP-Anwendungen an.

An der BFH sind bereits verschiedene Projekte zur Entwicklung einer STSCL-Standardzellen-Bibliothek durchgeführt worden. Wegen den differentiellen Signalen der STSCL, ist es bis jetzt nicht gelungen, die STSCL-Bibliothek in die automatisierten IC-Design Tools einzubinden.

In dieser Arbeit wurden deshalb ein spezieller STSCL-Workflow und die dafür benötigten Hilfsmittel entwickelt.

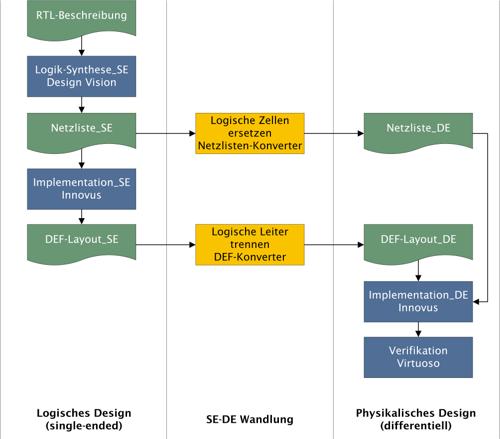

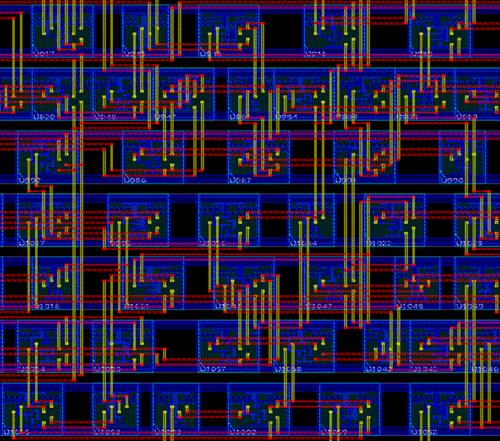

Der STSCL-Workflow (Abbildung 1) besteht aus einer logischen und einer physikalischen Designphase. Das logische Design basiert auf single-ended Varianten der STSCL-Zellen und umfasst die Synthese der Netzliste auf Gatter-Ebene, sowie die logische Implementation . Geroutet wird das logische Design mit breiten Leiterbahnen, welche als Platzhalter für die beiden Leiter eines differentiellen Signales dienen. Mit dem anschliessenden Ersetzen der logischen Zellen durch die realen, differentiellen STSCL-Zellen und dem Umwandeln der logischen Verbindungen in differentielle Leiterbahnen, entsteht das physikalische Layout. Für das Ersetzen der STSCL-Zellen und das Generieren der differentiellen Leiterbahnen, konnte in dieser Arbeit je ein spezielles Umwandlungs-Tool entwickelt und erfolgreich getestet werden. Abbildung 2 zeigt einen Ausschnitt aus dem Layout einer STSCL-Schaltung, mit den parallel geführten, differentiellen Leiterbahnen.